前言

懒癌发作,项目早就结束了。但是一直不想写。:smile:

先占个坑,以后再写完整。

项目需要用到一个镁光的flash,需要一个开源的qspi-flash控制器,连接到CPU上作为CPU外设。

感谢开源qspi-flash 控制器已经提供了比较完善的架构。

我需要做的主要有:

- 根据flash型号的差别迁移flash 的指令

- 根据项目需要将控制器的ahb接口转接到apb接口

- 迁移原项目中使用的IP,看不到源代码的IP都要被替换

- 替换项目中的存储器ram,与公司项目整体保持一致

- 搭建仿真环境,上板验证。

环境

-

FPGA开发板:ZYBO

-

软件:Vivado 2020.2、python3

-

开源qspi-flash 控制器(开源项目中的文档很详细,请仔细阅读)

正文

一、指令迁移

qspi_define.vh头文件定义了非编程模式下支持的指令译码。

根据芯片型号的不同进行修改即可。

qspi_inst_decode.v文件中定义了指令的译码,可以根据需要进行修改。

二、apb2ahb

apb只支持单次读写32字节,但是项目使用的控制器中的寄存器位宽并不相等。

使用apb读写寄存器可能会影响其他寄存器。

为了方便,修改apb接口层代码将每个寄存器位宽都调整至32位。但是寄存器的有效位宽还是和之前一样。

修改后的寄存器地址如下:

// FLASH REG ADDRESS

`define FLASH_REG_Divide 32'h00 //valid bit width 32

`define FLASH_REG_Ctrl 32'h04 //valid bit width 16

`define FLASH_REG_Csr 32'h08 //valid bit width 8

`define FLASH_REG_State 32'h0c //valid bit width 8

`define FLASH_REG_Addr 32'h010 //valid bit width 32

`define FLASH_REG_Data 32'h014 //valid bit width 32三、替换fifo mem

原项目提供了宏开关,FPGA 使用 Xilinx的IP。

IP很方便但是看不到源码,需要替换掉。好在也比较简单,只需要替换fifo中使用的ram就行了。

// synthesis translate_off

initial begin

for(i=0;i<255;i=i+1)

mem[i] = {WIDTH{1'b0}};

end

// synthesis translate_on

endmodule需要注意的是,ram中需要加上仿真清零语句。否则会导致不定态的传播。

四、Vivado命令行仿真

这部分是我一直想做但又不会做的部分。这部分参考了官方文档:ug900-160页

//切换到当前目录

cd %~dp0

//编译源文件

call xvlog -sv -i D:\work\sdk_test\micron_flash\design\qspi_controller\include D:\work\sdk_test\micron_flash\testbench\testbench.sv

call xvlog -i D:\work\sdk_test\micron_flash\design\qspi_controller\include D:\work\sdk_test\micron_flash\testbench\N25Qxxx_flash_model\N25Qxxx.v

//建立设计

// -realx 是必须的,他会忽略文件中没有仿真尺度的代码的问题

call xelab -relax testbench -debug typical

//开始仿真

call xsim testbench -gui -t sim.tcl 这个脚本在window中执行。

运行时需要先将vivado 的bin目录前加到可执行路径中。

因为xvlog\xelab\xsim都是外部命令,所以需要使用call调用。

call会等待命令返回后,执行下一条命令

不适用call,终端使用权移交外部命令后不会返回,只能执行第一条命令

可以在sim.tcl 中设置仿真的属性:

# 将所有的信号都存储起来,方便随时查看信号。

log_wave -r /

# 设置仿真时间,也可以 run all

run 2 us

# 指定仿真的波形文件

set_property xsim.view D:/work/sdk_test/micron_flash/scripts/work.testbench.wcfg [get_filesets sim_1]仿真的波形文件第一次可以先不设定,在gui界面中选择好后,保存。

供后面的仿真使用。

若想要重新仿真,就需要删除临时文件

cd %~dp0

rd /s /q .Xil

rd /s /q xsim.dir

del *.jou

del *.log

del *.pb

del *.wdbdel用于删除文件

rd用于删除目录

- /s 删除指定目录和所有子目录及其包含的所有文件

- /q 安静模式。删除目录时,不会提示确认信息

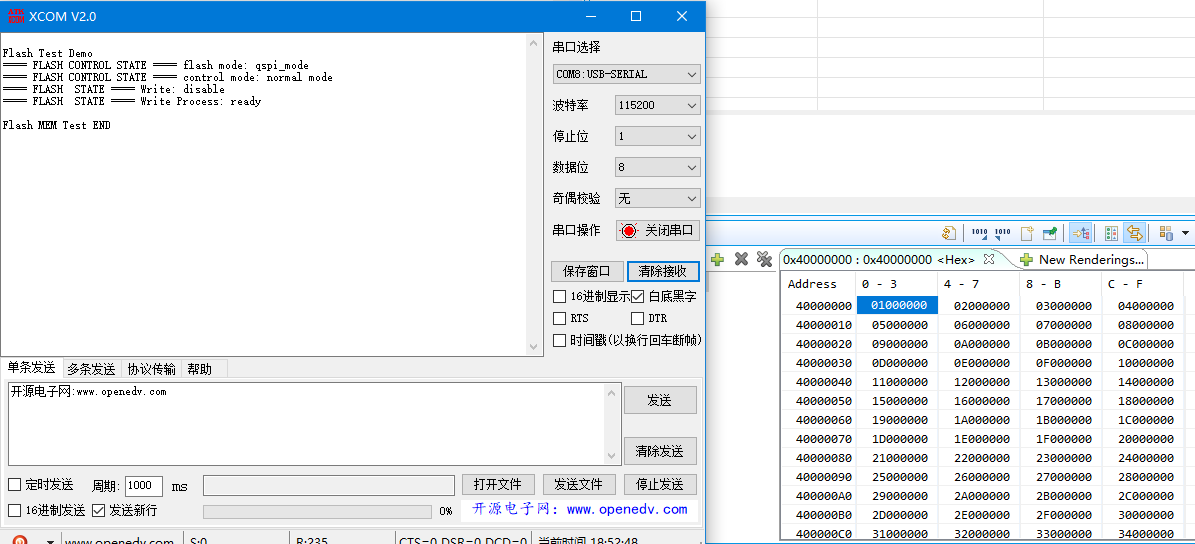

五、上板测试

在ZYBO上验证,验证的时候使用ARM硬核运行程序。地址从0x40000000开始。

测试了读出,写入和擦除。

附件

- 项目仿真环境开源:

- Gitee: micro-flash