从验证角度看UPF

从验证角度看UPF

序言

Unified Power Format (UPF)全称统一功耗格式,是专门用于描述电路电源功耗意图的一种语言标准。使用UPF命令,可以指定芯片的供电网络、电源开关、iso、retain和电源管理的其他方面。

UPF验证流程

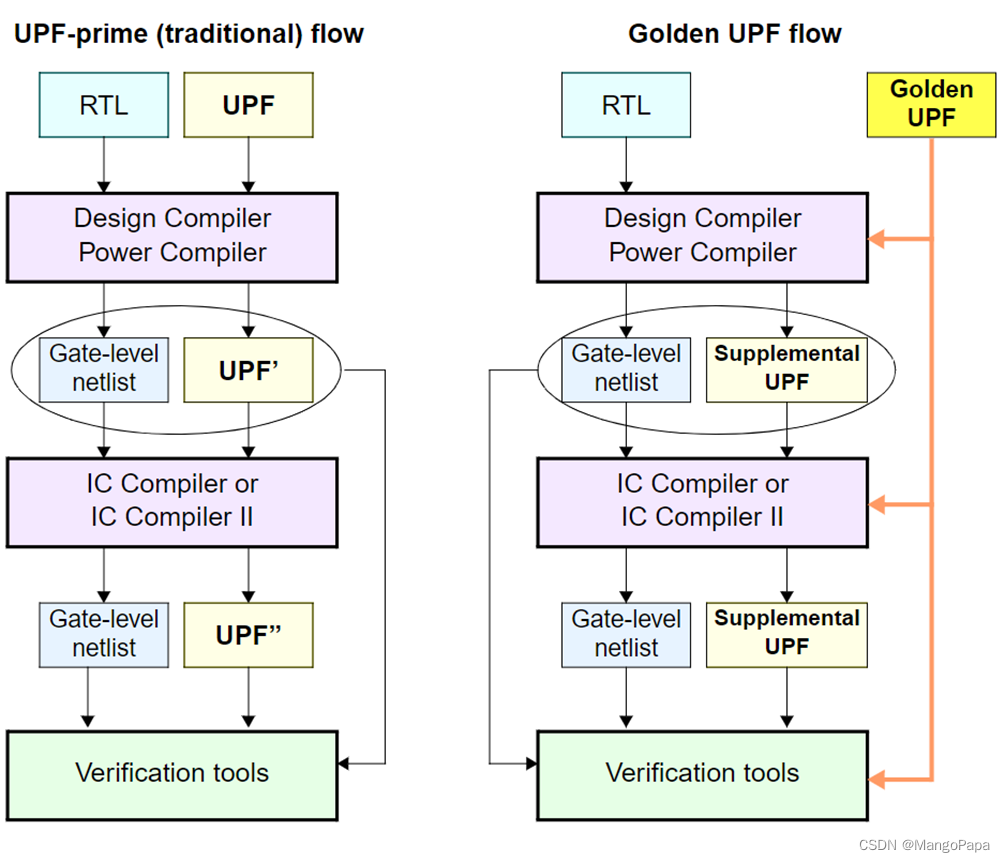

有两种常用的低功耗仿真 Flow:

- 一种是传统的

UPF-prime Flow,该 Flow 需要设计人员在不同阶段提供 3 个不同的 UPF; - 另一种是 Synopsys 推荐的

Golden UPF Flow,该 Flow 只需要在最开始提供一个能够在前仿和门仿中复用的 Golden UPF。

两种 Flow 流程图如下图所示。

上图UPF仿真分三个阶段:

-

RTL+UPF。 RTL 为综合前 RTL, 没有插入 Low Power Cell 和 PG Pin。 -

netlist+UPF。使用 DC 逻辑综合后的门级网表,已经插入了部分 Low Power Cell,但未插入 PG 和 Power Switch。 -

netlist+UPF 及 PG Netlist。采用物理实现后的门级网表+UPF。 或用带PG Pin的网表,已经包含了整个供电网络。

在NB2416、NB2413、NB2426系列项目中,使用的是右边的Golden UPF Flow。前仿真是RTL+UPF,后仿真使用带PG Pin的网表直接仿真。

具体验证流程如下:

- 架构人员确定整个芯片的电源规划,输出电源管理文档和UPF框图,描述整个芯片的功耗设计意图。

- 前端设计人员编写各个模块级和系统级的upf。

- 验证人员拿到前端的upf后需要在其基础上进行一定修改,修改后得到前仿真使用的upf。修改不改变原有的UPF意图。

- 搭建UPF仿真环境,修改TB,指定编译选项。

- 编写UPF验证case, 根据验证点写case。

- 收集覆盖率。

第一步:修改UPF文件

修改UPF只是为了满足验证的需要,并不改变原有的设计意图。修改的原因有三个:

-

修改部分语法:DC支持的UPF语法和VCS支持的不一样,修改是为了使VCS能正常解析UPF。

-

设置一些仿真属性。

-

使用

load_upf载入其他模块的UPF。新思交流时提到,

load_upf 建议使用绝对路径。实际测试发现不同版本对相对路径的解释不同。load_upf -scope U0_zcou_top /xxx/xxx/de_feint.upf -

设置 initial 块的

SNPS_reinit。默认情况下 initial 块只执行一次,为确保initial 块在下电后重新上电时能重新执行,需设置此选项。示例如下:set_design_attributes -attribute {SNPS_reinit TRUE} -models {model1 model2 model3} -transitive TRUE # 设置 -transitive TRUE 后,其他模块相关属性默认为 FALSE。 -

对 ROM 等不受 UPF 掉电影响的模块设置

UPF_dont_touch,确保其 Always On。set_design_attributes -attributes {UPF_dont_touch TRUE} -models {model1 model2 model3}

-

-

通配符展开:设计编写的UPF在指定电源域中使用了模块通配符,VCS解析通配符会花费大量的时间。将通配符展开可以显著加速。

展开前

connect_supply_net SS.power -ports */*/*/*/*/*/*/*_sram*/VDD展开后

load_upf /xx/xx/vpe_sram.upf

vpe_sram.upf的具体内容:connect_supply_net SS.power -ports /具体的路径/VDD

注意:UPF中的Hierarchy 用

/ 而非.

第二步:搭建UPF仿真环境

修改TB

在 TB 中开关电源,给指定端口供电。示例如下:

import UPF::*;

initial beign

supply_on("VDD", 0.72);

supply_on("VSS", 0);

end

添加UPF编译选项

-

指定 UPF 路径:

-upf <upf_file> -

指定 Power Top

- 通过 vcs 编译选项

-power_top <top_module_name> 指定; - 或在 UPF 中通过

set_design_top <tb/dut> 指定 Power Top。

- 通过 vcs 编译选项

-

指定相关 vcs 编译选项,

-power=<opt1>+<opt2>+…。- 如

-power=attributes_on+cov_pst+cov_iso+cov_psw,开启相关覆盖率收集

- 如

-

UPF相关的log和报告在编译目录下

mvsim_native_reports文件夹内。

第三步:编写UPF case

验证点1:检查电源域划分和UPF意图是否一致

原因

- 首先需要检查设计写的UPF和设计意图是否一致

- 其次因验证对UPF进行了修改(特别是通配符展开),需要确保验证使用的UPF和设计意图一致。

实现

-

方法一:人工检查。在verdi波形中人工check每个电源域。

缺点:麻烦、费力只适合TRY-RUN阶段。

-

方法二:脚本检查。

- 由DC生成gold的sram列表。

- 从编译过程中生成的编译后upf文件中提取各个电源域的sram列表。

二者比较,确保所有的sram都加入了PD_SRAM域。

- 缺点:需要DC配合,设计改动时需要DC及时更新sram列表,增加了维护工作量。

- 只能生成所有的sram列表,无法满足需求生成指定类型的sram列表。如带有repair功能的sram列表和不带repair功能的列表。

-

方法三:脚本检查

- 使用脚本自动生成sram列表。

其他和方法二相同。

- 缺点:gold也由验证生成。

- 优点:可以生成带有指定端口、寄存器、线网的模块列表。减少了交互,提升了效率。

验证点2:iso检查信号钳位

原因

需确保所有需要钳位的端口都正确插入了ISO。信号钳位值也都是正确的。

检查项:

- 模块掉电期间,掉电域输出X态。

- ISO大部分钳位到0,部分输出端口钳位到1,还有部分输出端口(scan、bist等)不钳位。

实现

特定模块特定端口的iso状态是已知的,使用简单的if判断即可实现。实现上遇到的困难主要是:

- 不同模块钳位检查的端口不一样

- 模块类型多,模块输出端口多,要写的检查代码太多。

最后也是使用脚本批量生成的。这样如果RTL有更新,也可以使用脚本较快的生成相关的检查代码。

验证点3:控制信号连接性检查

原因

确保寄存器的控制信号正确连接到各个SRAM的控制端。主要是:

- pwr_en --> sram的SD端口,sram的FISO端口

检查项有:

-

上电时:

- SRAM的SD端低电平

- SRAM的FISO端高电平

-

下电时:

- SRAM的SD端高电平

- SRAM的FISO端低电平

实现

单个端口的检查代码,使用简单的if判断即可实现。遇到的困难和iso检查信号钳位时也基本相同。

最后也是用脚本批量生成。

验证点4:sram的repair信号掉电保持

原因

确保sram的shift_reg放在了always_on域,repair信号掉电后能保持。

检查流程:

- 掉电前:给sram的shift寄存器写一个随机值。

- 掉电后重新上电:检查sram的shift寄存器的值是否是写入的随机值。

实现

实践中发现shift寄存器的不同bit位有不同含义不能简单随机,经测试可随机低8bit(和库单元相关,其他项目不适用)。

同样也是用脚本批量生成相关检查代码。

验证点5:掉电和上电流程

原因

确保芯片重新上电后能正常工作。

检查流程:

- 部分掉电,随机掉电阵列。

- 适用未掉电的核跑网络。

- 全部上电,再跑网络。

同样可以检查各个电源域之间的隔离情况,确保掉电域不会影响上电域的工作。

验证点6:其他电源控制功能

和项目相关,具体问题具体分析。

脚本生成检查代码的几种方法

UPF相关的检查项特点是检查项多,但单个检查项简单。适合适用脚本批量生成。在项目中前后使用过几种方法:

-

方法1:使用

verilog-perl模块,解析RTL代码,结合一些参数生成UVM检查代码。- 缺点:不支持

generate语法,前仿真需要额外处理。后仿真可以直接用。 - 优点:perl脚本调库实现,性能较好。

- 缺点:不支持

-

方法2:使用

slang工具,解析RTL代码生成语法树json文件。然后使python解析json,结合一些参数生成UVM检查代码。-

缺点:

- 太消耗内存,前仿还行,后仿根本跑不动。

- 生成的json文件体积大,python解析时间长。

- 需要额外编写规则,解析语法树json文件。

-

优点:支持解析

generate,对SV特性支持较好。

-

-

方法3:使用

VPI,编写C程序,调用VPI接口。基于VCS解析RTL代码。对语言特性支持最好。-

缺点:

- 不能单独使用,需要结合VCS以及ucli命令行使用。

- 使用C编写,难度较高。

-

优点:

- 速度极快:在NB2426(10亿门)中也是秒出结果。

- 和VCS能保持一致性,保证解析内容和实际仿真结果符合。

-

其他

verdi查看UPF

适用verdi可以直观的查看电源框图(verdi可自动生成),模块power domain,插入的iso单元,信号钳位等相关信息。经项目实际操作以及和新思沟通,推荐适用-dbdir的方式打开verdi,这样能较好的保证和vcs仿真的一致性。若用verdi吃file list的方式打开,UPF相关往往不能正常显示(power domain图标显示错误、模块和电源域对不上、钳位端口显示错误等)。

新思推荐使用

-dbdir的方式打开verdi。新版本verdi也仅支持这种方式。编译时添加参数

-kdb,会在编译目录下生成一个simv.daidir目录。使用命令行verdi -dbdir /XX/XX/simv.daidir即可打开。实例:

verdi -dbdir vcsworks/case_comp_upf/simv.daidir

查看UPF相关覆盖率

因电源域较多,UPF相关的覆盖率也较多,直接使用网页查看显示不全。可生成文本格式的覆盖率报告查看或使用其他软件查看(如verdi等)。

减少后门路径使用

UPF的检查代码中大量使用了后门路径,当设计规模较大时(10亿门),大量的后门路径会消耗大量的内存(1.5TB)。应尽量减少UPF检查代码中后门路径的数量。如:NB2426系统级仿真中,只检查ZG340/ZG30S的端口。其子模块不再单独检查。

Comments 1 条评论

才开始写博客么,加油加油!